「DC-DCコンバータのEMI発生メカニズムとその対策(第3回)」ではスイッチング方式DC-DCコンバータ回路におけるEMI対策手法について説明します。

本シリーズの第2回では、昇圧DC-DCコンバータ回路の動作に伴い観測されたEMIに着目し、その発生要因としてFETがOFFの際に構成される「ホットループ」に関わる回路の共振が関与していることを示しました。今回(第3回)はこの「ホットループ」回路に着目し、EMI抑制手法について考えます。

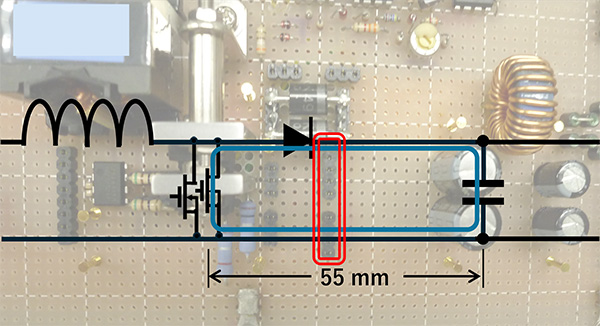

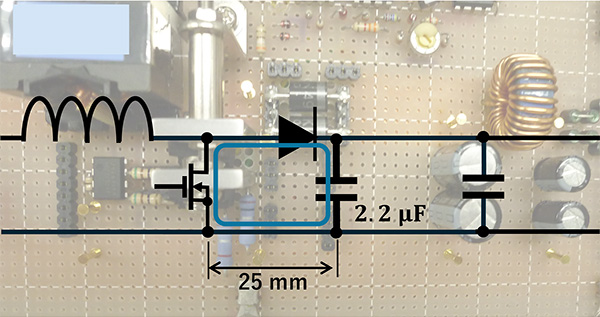

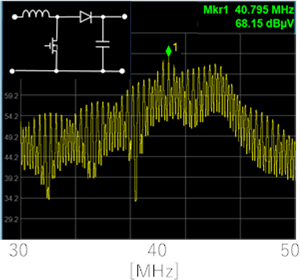

ループ状の高周波の電流は電磁波を発生します。その強度はループの形状が波長に比べて十分に小さい場合(微小ループ)、面積に比例することが知られています。したがって、ホットループの面積の縮小によるEMI低減が期待できます。今回の評価に用いている基板は図1(a)の赤枠で示す位置に部品搭載用のソケットが設けられており、このソケットにコンデンサを挿入し、高周波の電流を誘導することで、図1(b)に示すようにループ面積は45%に低減されます。図2にコンデンサの適用前後のEMI特性とコイル出力端の電圧VAの波形を示します。EMIがピークとなる周波数は40.8MHzから49.8MHzにシフトし、レベルは約5dB低下しました。なお、EMIレベルがループ面積に比例すると仮定すれば、20×log10(0.45)=-7dBとなり、この値に近い低減効果が得られたことがわかります。

次にレベルがピークとなる周波数の変化をみてみます。VAにおけるリンギングの波形は周期が25nsから20nsに変化し、ピークの高周波側へのシフトとほぼ一致します。この理由はループ面積の縮小によるループの自己インダクタンスの低下と考えることができます。

なお、文献(1)を参考にしてサイズが55mm×20mmのループと、25mm×20mmのループの自己インダクタンスを計算したところ、それぞれ、155nH、90nHとなりました。追加したコンデンサのESL(ここでは5nHとします)を含めるとその共振周波数は約50MHzとなりEMIのピーク周波数のシフトを説明することができます。

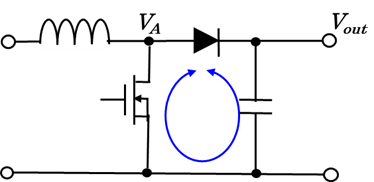

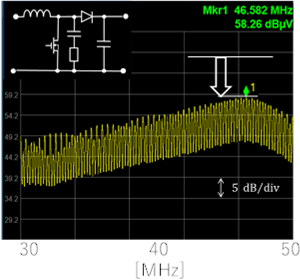

スナバ(snubber)回路は抵抗(R)とコンデンサ(C)を直列に接続した回路で、一般に、電子回路のスイッチング時のノイズやサージ電圧の抑制に利用されます。RCスナバ回路はスイッチング素子と並列に配置することで、スイッチング時に発生する電圧スパイクやリンギングを抑制します。

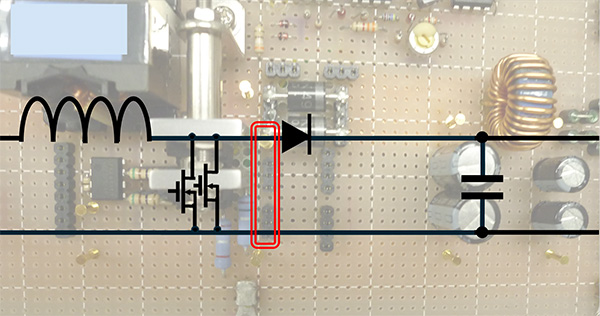

この回路モジュールでは図3に示すように、FETスイッチに並列に設けられたソケットに抵抗RとコンデンサCで構成されたRCスナバ回路を挿入します。今回、用いたスナバ回路の抵抗は6.7Ω、コンデンサは10nF、カットオフ周波数は2.3MHzです。

スナバ回路挿入によるEMI特性の変化を図4に示します。スナバ回路の適用により共振の影響が低減され、EMIレベルはおよそ10dB低下しました。なお、スナバ回路の適用にあたっては適切な素子を選択するとともに、効率の低下に注意する必要があります。

(a) スナバ回路適用前

(a) スナバ回路適用前 (b) スナバ回路適用後

(b) スナバ回路適用後3回に分けて、DC-DCコンバータ回路におけるEMI発生メカニズムとその抑制対策についてモデル基板による実測の結果を交えながら説明して参りました。

DC-DCコンバータではスイッチング素子を含むホットループにおける共振が高いレベルのEMI発生の要因であることを示しました。この共振の特性には、主にFETがOFFの状態におけるソース―ドレイン間の寄生容量、また、配線のループインダクタンスやキャパシタの等価直列インダクタンス(ESL)などの回路図には記載されない寄生成分が大きく影響します。

DC-DCコンバータのEMI抑制対策のためにはこのホット―ループに着目し、そのループ面積を小さくすること、また、各素子の寄生成分や配線のインダクタンスを可能な限り把握して共振の特性をコントロールするなどの対応が必要です。